<Memory addressing>

memory "address" is also a 32-bit (non-negative) integer.

memory -> register: Load

(need address & destination register)

register -> memory: Store

(need address & source register)

<Memory Operand>

C code 1:

g = h + A[8];

g in x1, h in x2, base address (starting address) of A in x3

A is an 'int' type array

(array: list of values)

Compiled RISC-V code:

Index "8" requires an offset of 32

lw x10, 32(x3) # lw = load word

add x1, x2, x10

첫 번째 줄 x10: destination register

32: integer value

x3: register number

32(x3): represent address part

C code 2:

A[12] = h + A[8];

h in x2, base address of A in x3

Compiled RISC-V code:

lw x10, 32(x3) # load word

add x11, x2, x10

sw x11, 48(x3) # store word

세 번째 줄 x11: source register

48: offset value

x3: base register

lw와 sw는 방향이 다르다는거 기억하기!

lw는 32(x3)을 x10에 load (오른쪽에서 왼쪽으로)

sw는 x11을 48(x3)에 store (왼쪽에서 오른쪽으로)

C code 3:

for ( i = 0; i < 10; i++ ) {

sum = sum + A[i];

}

sum in x1, i in x2, base address of A in x3

Compiled RISC-V code (only the loop body):

addi x10, x10, 4 (everytime we go th the for loop, actual memory location increase by 4)

lw x11, 0(x10)

add x1, x1, x11

<Memory>

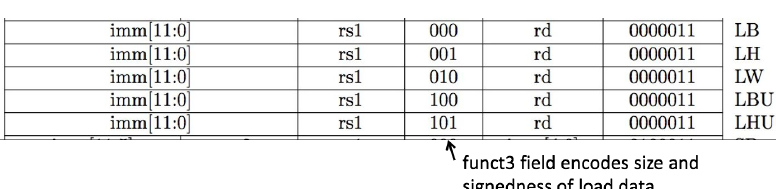

lw, lh, lb

load word / halfword / byte

sw, sh, sb

store word / halfword / byte

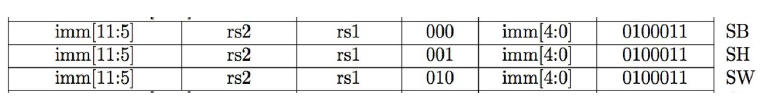

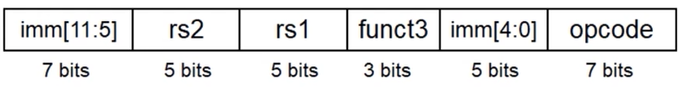

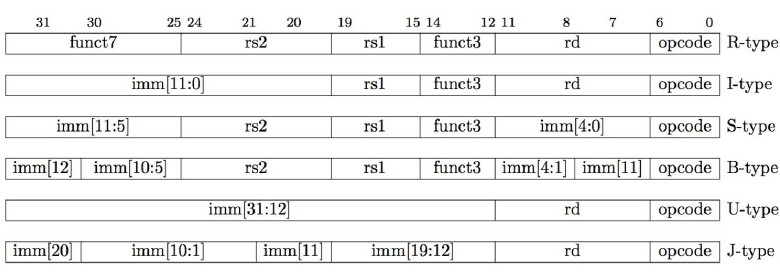

<RISC-V S-format Instructions>

Store instructions use a different binary format:

rs1: base address register number

rs2: source operand register number

immediate: offset added to base address

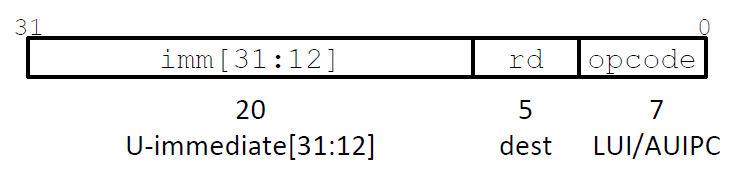

Most constants are small

For occasional 32-bit constant,

lui rd, constant

Load Upper Immediate

copies a 20-bit constant to [31:12] of rd (upper 20 bits of data)

sets the lower 12 bits of rd to 0

<Sign Extension>

RISC-V instructions sign-extend the immediate value

lh and lb also sign-extends the loaded halfword or byte

lhu and lbu zero-extends the loaded halfword or byte

-> regardless of loaded value, always fills remaining field with 0

There are no shu or sbu instructions.

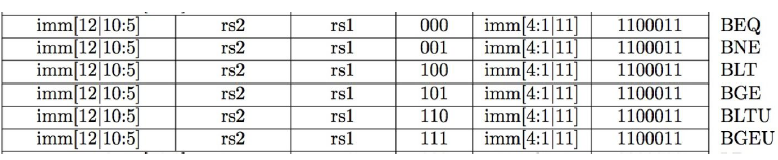

<Conditional Operations>

Branch to a labeled instruction if a condition is true

Otherwise, continue to the next instruction.

(Depending on condition, if condition is satisfied, it actually jump to another location)

If we want to write program structure like conditional statements, while / for loops,

we need to let CPU where we want to move after executing the such instruction - change order of execution

beq rs1, rs2, L1

if (*rs1 == *rs2), jump to the instruction labeled L1

bne rs1, rs2, L1

if (*rs1 != *rs2), jump to the instruction labeled L1

ex)

beq x10, x12, L1

: If x10 and x12 have some value, then next instruction we're going to execute is indicated by L1 label

There is no destination register

blt rs1, rs2, L1

if (*rs1 < *rs2), jump to the instruction labeled L1

(less than)

bge rs1, rs2, L1

if (*rs1 >= *rs2), jump to the instruction labeled L1

(greater or equal to)

signed comparison: blt, bge

unsigned comparison: bltu, bgeu

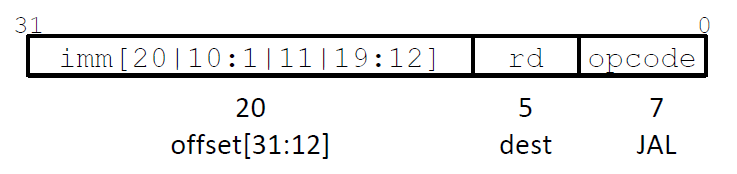

<Jump Instructions>

jal x1, L1 : jump-and-link

jump to L1

Address of the following instruction (PC + 4) -> x1

여기서 PC + 4 는 address of the following instruction을 의미한다.

similar to 'function'

- branch instruction과 jump instruction의 차이 -

In branch instruction, if condition does not match, we can just go to next instruction

but in jump instruction, we always jump to the target location

쉽게 생각하면 brach는 if ~ else문, jump는 함수를 생각하면 되겠다.

if ~ else문은 조건에 충족할 경우 이를 수행하지만, 함수는 어떤 조건이 있지 않다.

다른 location으로 jumping 하면, we have to know where to come back.

: that's why we are remembering location to come back jumping to another locaiton

-> why we are performing additional link operation that stores following instruction's address

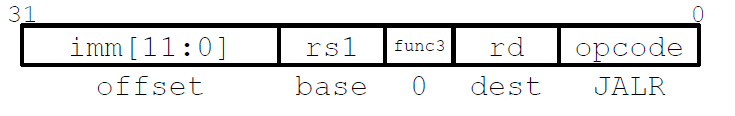

jalr x1, offset(x2) : jump register

jumping to the address stored in the register

jump to offset + address in x2

Address of the following instruction (PC + 4) -> x1

j L1 : jump

pseudo-instruction

jal x0, L1

PC: value that tracks where we are executing the instruction from the memory

'SKKU SW > Computer Architecture' 카테고리의 다른 글

| [컴퓨터구조] 5. Memory Hierarchy 메모리 계층구조 (0) | 2023.05.28 |

|---|---|

| [컴퓨터구조] Procedure Calling (0) | 2023.04.17 |

| [컴퓨터구조] RISC-V Instruction Formats(1) (0) | 2023.04.14 |

| [컴퓨터구조] Logical operations (0) | 2023.04.14 |

| [컴퓨터구조] Immediate Operands, Load Immediate Value (0) | 2023.04.14 |